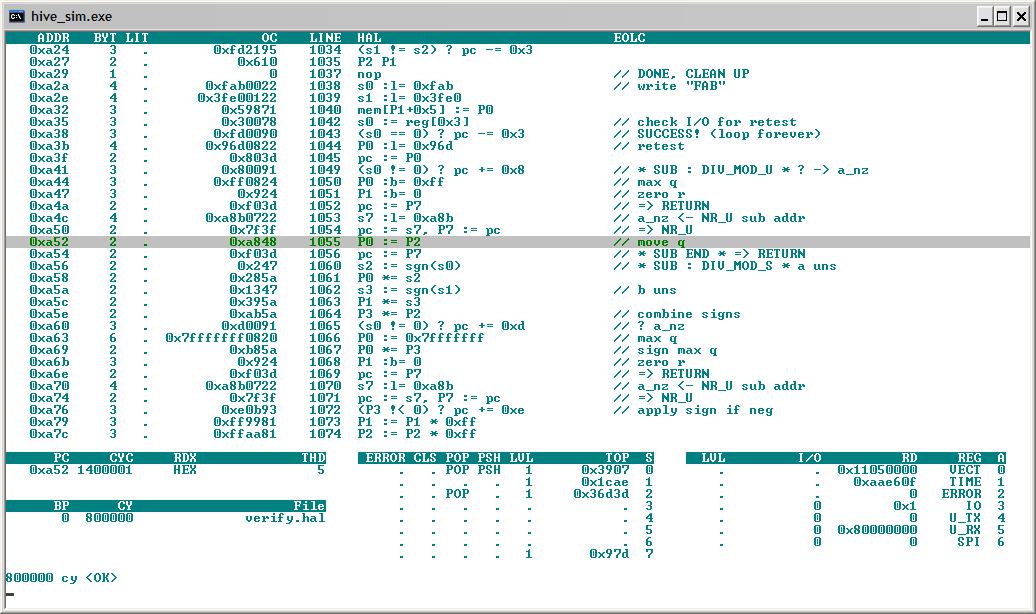

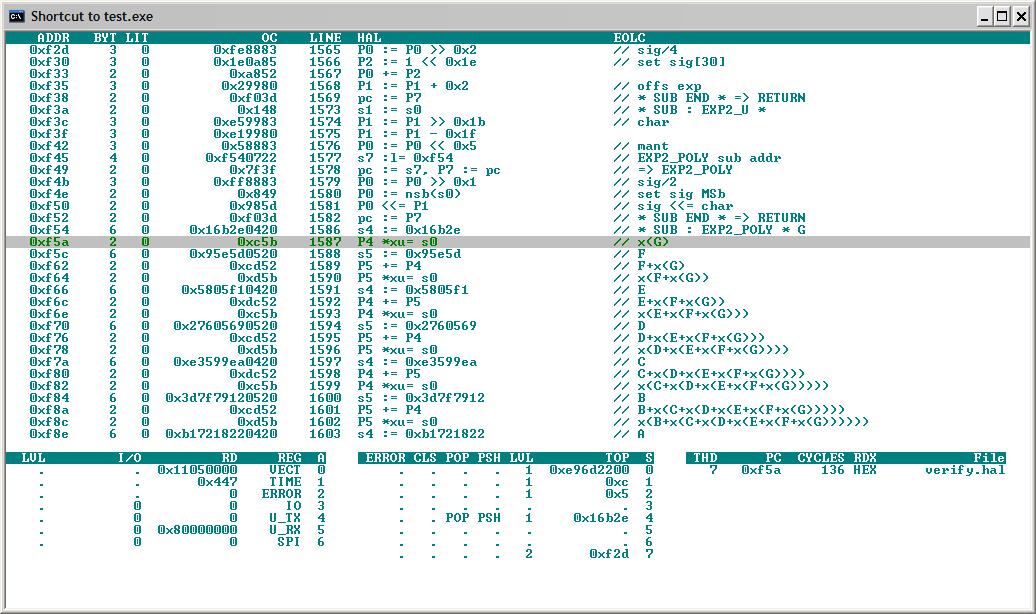

Thought you might like to see the sim so far:

The listing for thread 7 is above, at lower left is the register set (with only the basic core registers shown, none of the Theremin registers), at lower center is the stacks status for thread 7, and at lower right is some info / sim status. I'll probably swap the register and info views to make room to view more registers on the lower right with the command line on the lower left.

In the listing display, the "BYT", "LIT", and "LINE" columns are new, they show how many bytes are in the opcode, whether the opcode is a literal or not, and what line in the sourcecode the opcode came from (extremely useful). Note the explicitly variable lengths in the opcode column now.

The command line code isn't implemented yet (only doing single key stuff at the moment to prove the core and display) and I'm not sure if there will be any screens other than this one because I want to keep it really simple. For the current single key stuff (which will likely change somewhat) the number keys select the thread to display, the 'c' key does one clock, the spacebar does 8 clocks, the 'h', 'u', and 'i' keys pick the display radix, and the 'q' key quits the sim. I need ways to interact with the UART FIFOs, GPIO, and SPI; load a different *.hal file; issue core clear and external interrupts; and page/scroll through the memory listing display without execution. (I wish IBM had started the function key numbering at F0 rather than F1...)

The new sim snags pertinent state info for each thread when it crosses from stage 7 to stage 0 in the pipeline. This way the state info remains stable throughout an 8 clock thread cycle for display purposes. In the old sim the displayed state was dependent on the stage you were viewing, which was realistic, but cumbersome and a little confusing - after changing the thread view I usually had to do several single clocks to get past stage 5 where the fetch happens in order to see the next state.

===========

[EDIT] Wow, this thread got ~500 views in 24 hours. Kind of hard to believe there are that many people in the world, much less visit here, with the intersecting interests of Theremins and soft processors. Bots? Web page scraping?