HW / SW Phase Lock

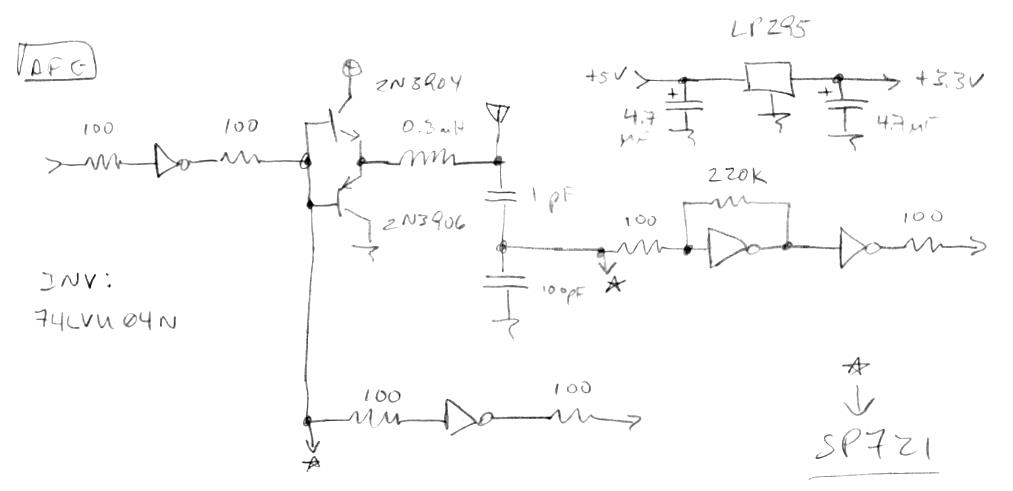

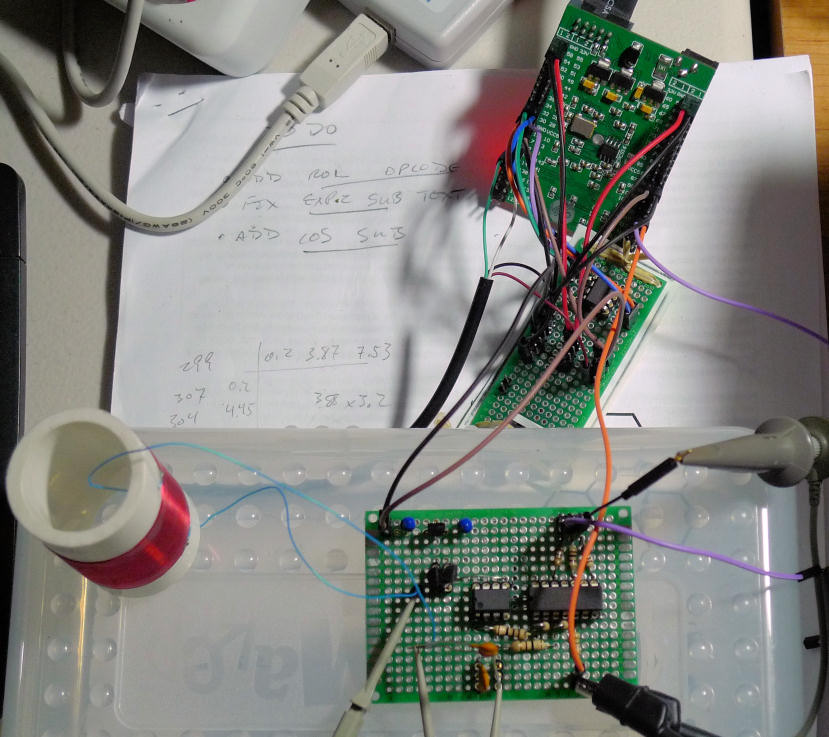

Got hardware phase lock yesterday via software in the loop - a first for me anyway. The processor's thread 7 external interrupt lead is connected to the internally generated SPDIF 48kHz frame signal, so on every interrupt it reads the phase error (which is 4th order filtered in the hardware to -3dB @ ~1kHz low pass), accumulates it, attenuates it, and writes the resulting value to the numerically controlled periodic delay, which drives the LC tank. The numbers are stored in Hive memory which I can manipulate via the Hive command line interface, so I've been playing around with it quite a bit. At the moment the setup still looks like the photo a few posts above, with a 10pF dummy antenna.

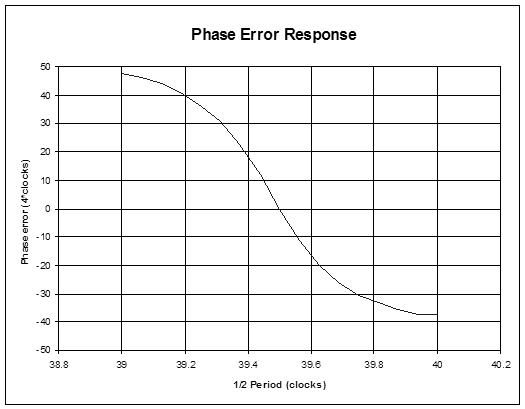

I'm seeing nice quadrature even if I grab the coil with my fingers and thus drastically lower the Q. It won't start up without having the initial values somewhat in the ballpark, but I haven't seen it lose lock after that. I have a script that walks through a series of attenuation factors which sets the loop cutoff higher and higher with each mouse click on the script dialog box button and it's very interesting to see the interaction of the Q based gain with loop stability (see the graph 2 posts up). With gains that are on the border of stability, the instability is only AROUND the lock point, but as the phase error bobbles away from the lock point, stability clearly returns and tries to restore quadrature lock, but this causes the Q to increase and therefore the loop gain to go back up, which decreases stability, etc. so it acts like one of those pendulum gravity vs. repelling magnet executive toys.

I've also experimented with 4th order phase error low pass filtering via software. It's pretty trivial to do, but it doesn't seem to improve things much, other than a general lowering of the feedback bandwidth - a gain thing more than anything else. With this filter set to -3dB @ ~500Hz, the edge of loop stability is with an accumulator gain of 2^-12, which is quite a bit more loop gain than I was thinking was likely to work in a stable manner (but I haven't worked the math yet).

Also just experimented a bit with a software high Q comb filter to kill 60Hz, but it seems to make things somewhat noisier and less stable. Maybe putting it inside the feedback loop is a mistake? I've had high hopes for that filter, but I haven't messed with it enough to know if it will be useful or not, or even if I've implemented it correctly in software.

Anyway, almost no matter what I do I'm seeing ~200ns of jitter out at 50ms trigger delay, which is ~4ppm or so and somewhat more than I would like. I'm sure using a real antenna this will be much worse, need to hook one up and see what range of stable numbers it can give. This jitter could be coming literally from anywhere: environmental pickup, the fan on my PC, thermal noise in the logic inverter, dither noise in the NCPD, timing slop due to different clock domains and interrupts, etc. I'll try to track it down, but everything is so exquisitely sensitive that may be impossible.