livio,

I think one can instantly see how heterodyning is hugely superior if you think about it this way..

Whatever your frequencies are (for the antenna oscillator) you are not going to get a deviation of more than perhaps 10% as a result of (wanted) player / control capacitance..

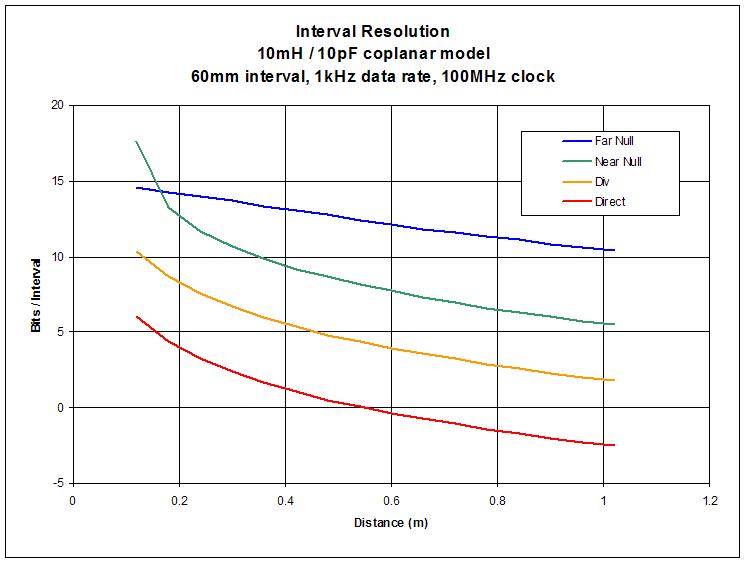

So one must capture "data" which is 90% redundant - as in, any clock used to count the period of a directly devided HF oscillator must be ~10 times faster than a clock used to count the period of a heterodyned signal (where the difference - ie ONLY the wanted is pre-resolved) in order to get similar resolution to that obtainable from a heterodyned (difference) signal.

My focus has been on analogue, so actual counting of period in order to derive a digital value is something I only have limited expierience of - however I have done some work in this area - originally 6 years ago when I was heading the digital route, and more recently to extract data in digital form for other functions.. My method was to take both reference and variable oscillators and independently multiply these with PLL's, and then heterodyne the results.. Using a *10 multiplier, the difference frequency (after heterodyning) is 10* the audio frequency of the unmultiplied oscillators (the oscillator difference frequency) ... So a 20Hz audio gives a 200Hz multiplied frequency that can be measured directly with a fast clock, and has low latency (5ms for a 20Hz audio, 500us for a 200Hz audio) -

One can (as you can) reduce the PLL multipliers to get higher resolution - a *5 multiplier is about the lowest acceptable, giving a 10ms latency @ 20Hz (audio) (the multiplied difference being 100Hz) and reducing as frequency increases (at 100Hz audio, multiplied difference is 500Hz, latency is 2ms - at 1kHz audio, multiplied d = 5kHz, latency = 200us)

I use the above system mostly to drive analogue period to voltage circuits (to derive a CV output) - as this scheme allows tracking of the theremins output frequency right down to 16Hz at low latency (unlike converters that act on the theremins pitch, and dont work below about 100Hz) -

If I was to seriously go to a digital "engine" I would probably use the above scheme with an ADC (as this would allow me to retain at least one beloved analogue heterodyned voice ;-) - probably using the MCU/FPGA to perform the exponential conversion (at present I use analogue exponential converters which are a pain) for any digital voice pitch resolution, CV output, and On-Key-Emphasis (which is my main reason for looking at digital at all).

But, at the end of the day, with a biased offset frequency heterodyning system, one gets effectively what I get using frequency multiplication (and from Dewsters plots, it seems you get great improvement in linearity) and the concequential low latency and high resolution..

I want to keep my conventional analogue heterodyning voice, so "biasing" the "null" point is not an option for me.. But for "grabbing" data if you are not using the heterodyned difference for direct output, I can see no other method which comes anywhere close..

Please note though - I am not a digital "guru" and I am a mathematical moron, so much of what you and Dewster have been discussing is at the edge of my full comprehension.. It is entirely possible that my calculations are wrong, or that I am missing something ~ but right now I have no idea what that might be if I am ..

Fred.

"Please, indicate the method you use and the frequencies to let me calculate your resolution."

The frequencies I use for my oscillators is almost irrelevant - but because I like to keep my PLL oscillator frequencies well below 8MHz I tend to run somewhere 'round 500kHz (I also do mixed signal register switching, which involves division of the oscillator frequencies - so dont run much below 400kHz, as the resultant divided frequencies become more difficult to filter if they drop below 100kHz)

There is no relationship between oscillator frequency and resolution - there is only a relationship between difference frequency / clocking frequency and resolution.

"For me a true Digital Theremin should't use hetherodyning and audio signal."

LOL ;-) .. So now were getting a whole new dimention ;-) Once we were arguing about what a "true theremin" was, and digital certainly didnt qualify, now were going to argue about what a "true Digital Theremin" is - And try to say that the most efficient method of deriving the required data is not usable for this new evolution, because its "unworthy" of the digital "ideal"..

Im putting my analogue jacket on and going for a walk down my analogue street - oh, not to forget my analogue wellies for the floods from the analogue river that has overflowed due to the analogue weather patterns we have completely fuc*ed up on the way to our digital utopia..