The Hardwareing: LED TUNER

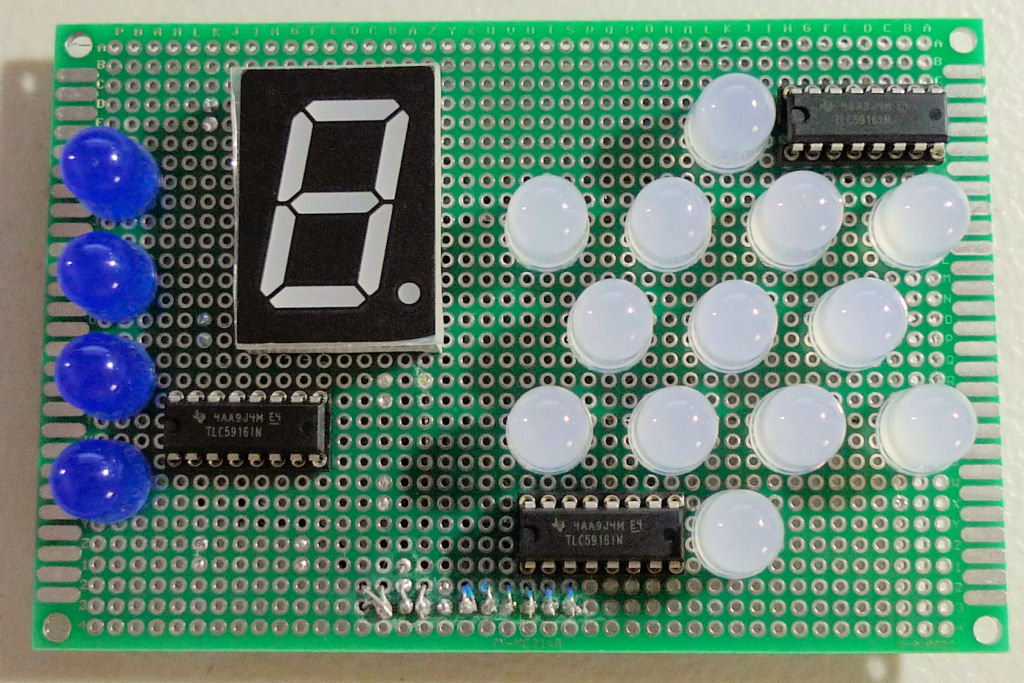

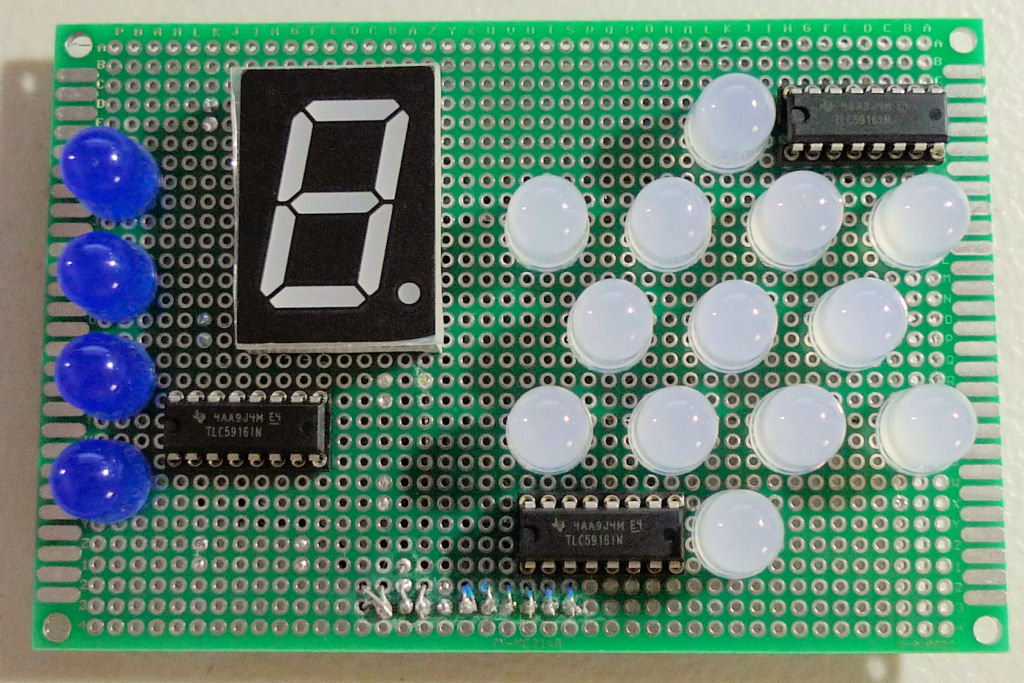

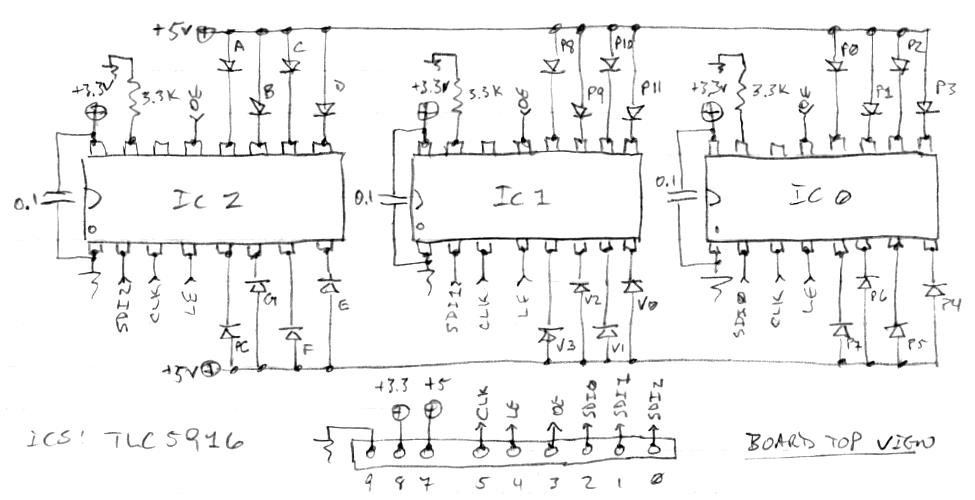

The pitch & volume display circuit is really simple. Just three TCL5916 ICs with decoupling and current set resistor, and a bunch of LEDs. I used 10mm high brightness white for the note and blue for the volume.

The note display has C located at the 10 o'clock position, which gives a nice vertically symmetric pattern for the key of C and Am. I have a couple of modes for it in the software, but only use the positive mode (note = LED on) with a bit of hysteresis, and the center LED is always on.

The volume display is implemented as a thermometer type in the software, with 12dB per LED, which works out well as the threshold of audibility seems to be around -48dB. 4 LEDs here, particularly with PWM, seem entirely sufficient in terms of resolution.

The 7 segment octave display is a 1" tall common anode higher efficiency red - beware that very often larger 7 segment displays have two diodes in series per segment, and using anything other than red for a two diode type will probably raise the forward voltage too high to work at 5V LED supply. The one I used is a single diode per segment type.

All LEDs have PWM applied in software to dramatically increase the resolution and make it all operate a lot smoother, including the octave display, which transitions between B and C.

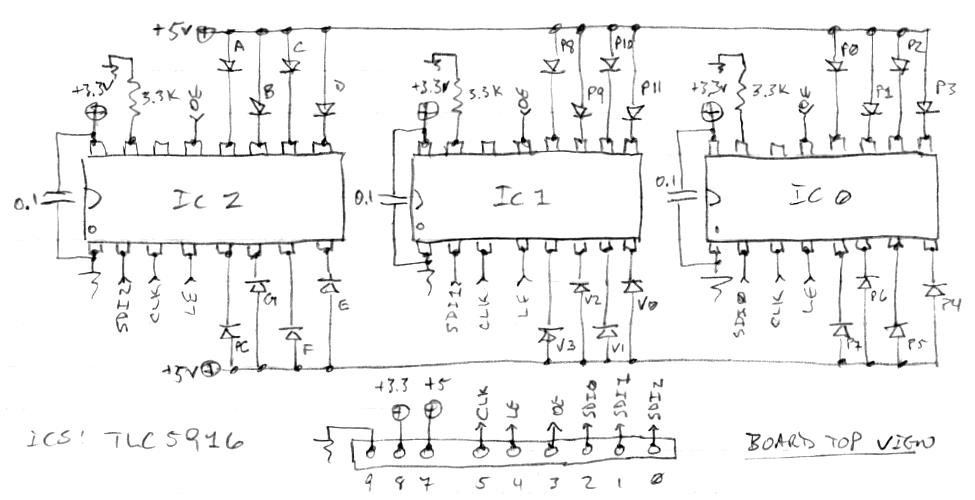

The minimum brightness is set via the 3.3k resistors, you might try 4.7k to go even lower if your LEDs are really high efficiency. There is a knob on the tuner UI page that adjusts the brightness via the TLC4916 "special" mode. I wired the LED outputs in reverse order than they are labeled in the datasheet to make them little endian, which is a better match for the "special" mode which is little endian (why the mixed modes in something so simple?). Inside the FPGA I'm driving three serial data lines in parallel, which speeds up the transfer and is just about as simple as anything other configuration. I'm always leery of race conditions when cascading serial devices, so that is studiously avoided here.

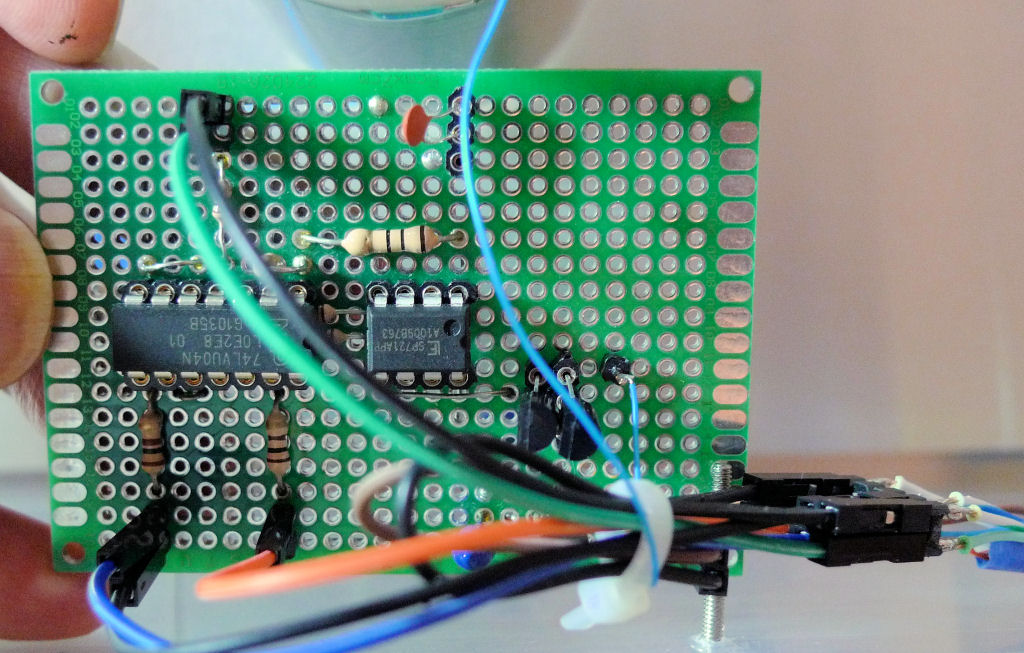

The front of the board. The ICs and silver pads are quite visible here which is kind of unfortunate. It would be nice to have a purely black background for the LEDs to increase the contrast.

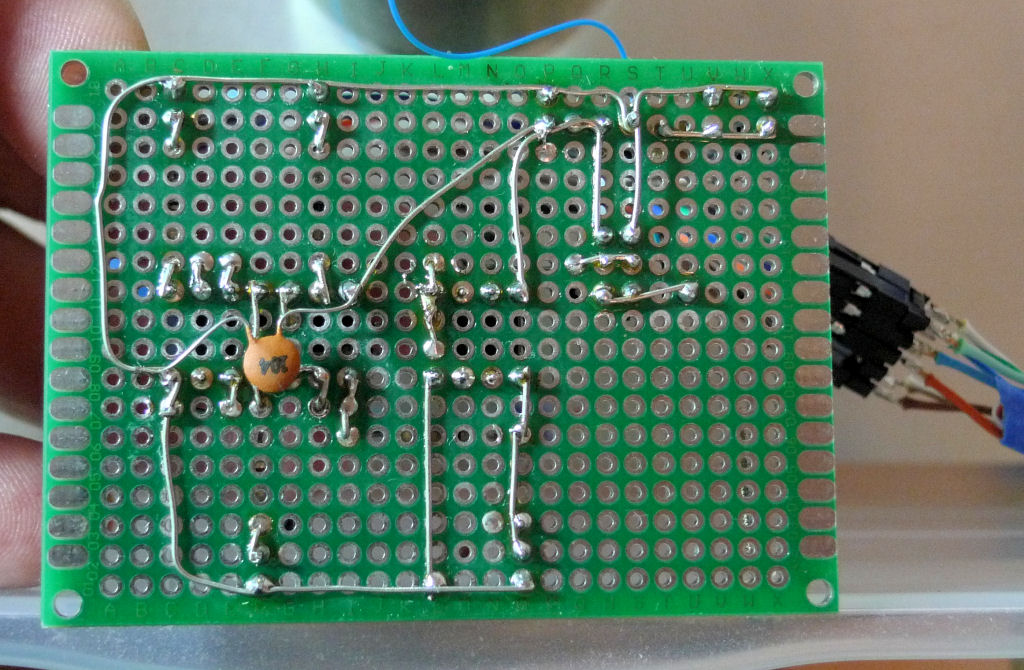

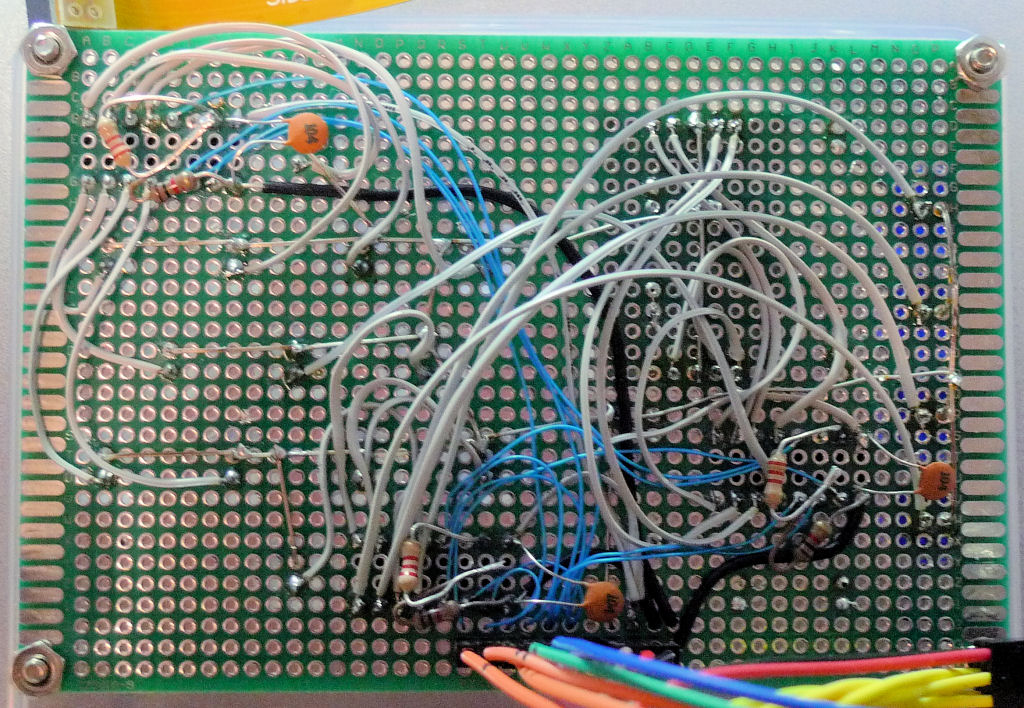

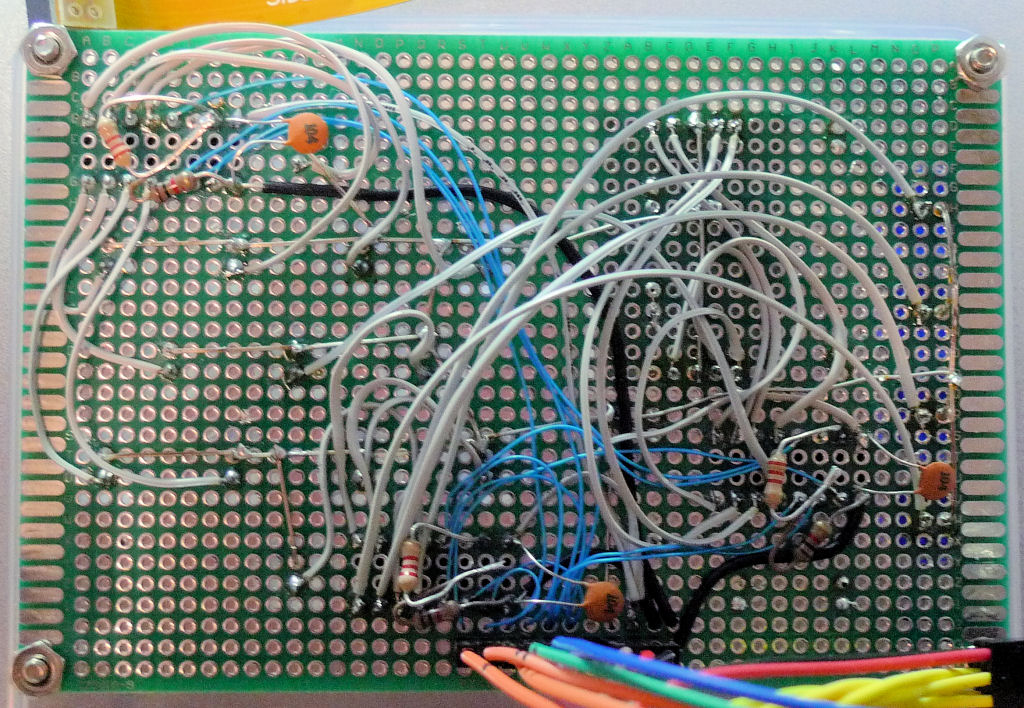

The back of the board is a rat's nest of wires, but that's about it. The reason you see 6 resistors here is I used 2.2k + 1k in series (was adjusting the current and never replaced the two with a single 3.3k).

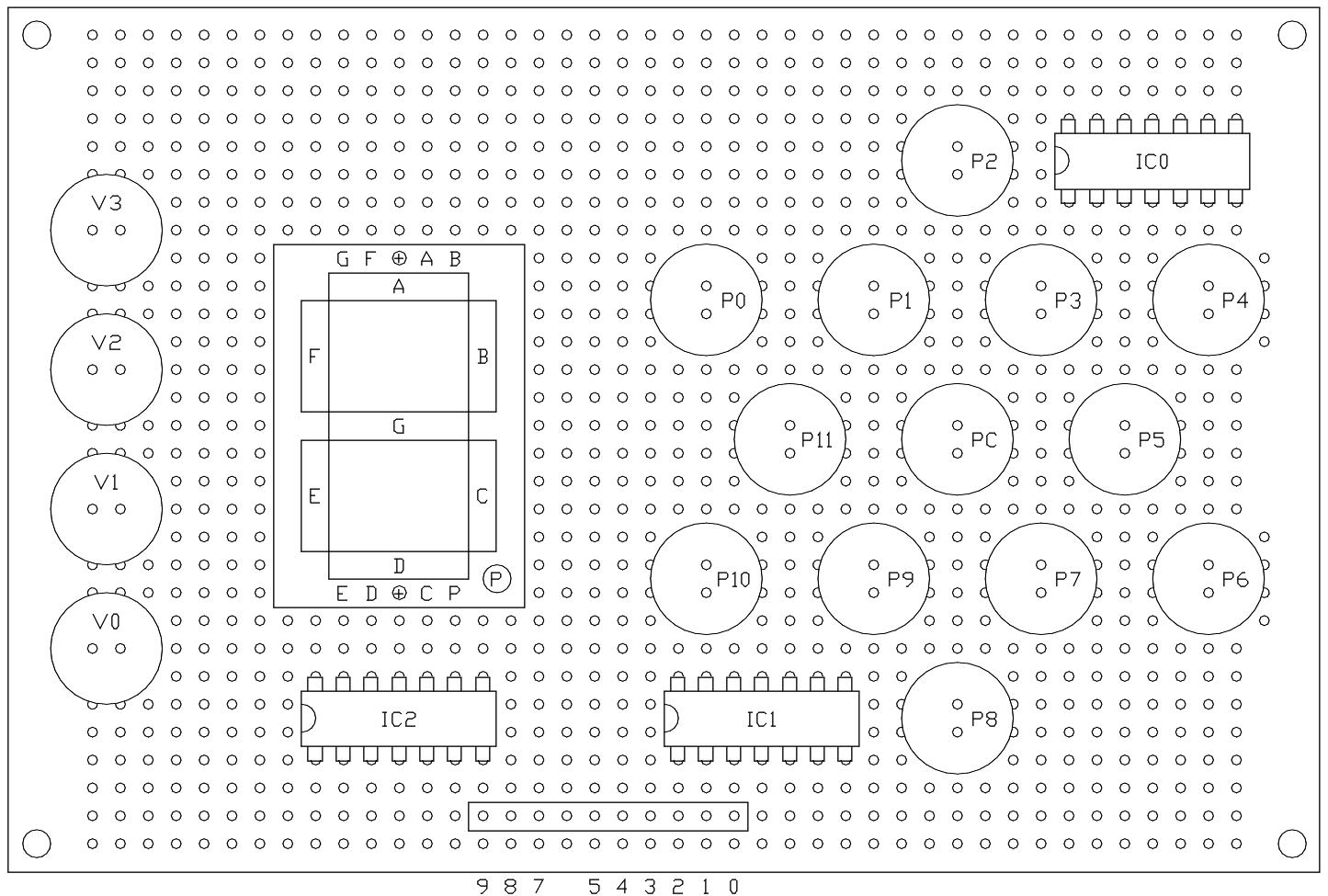

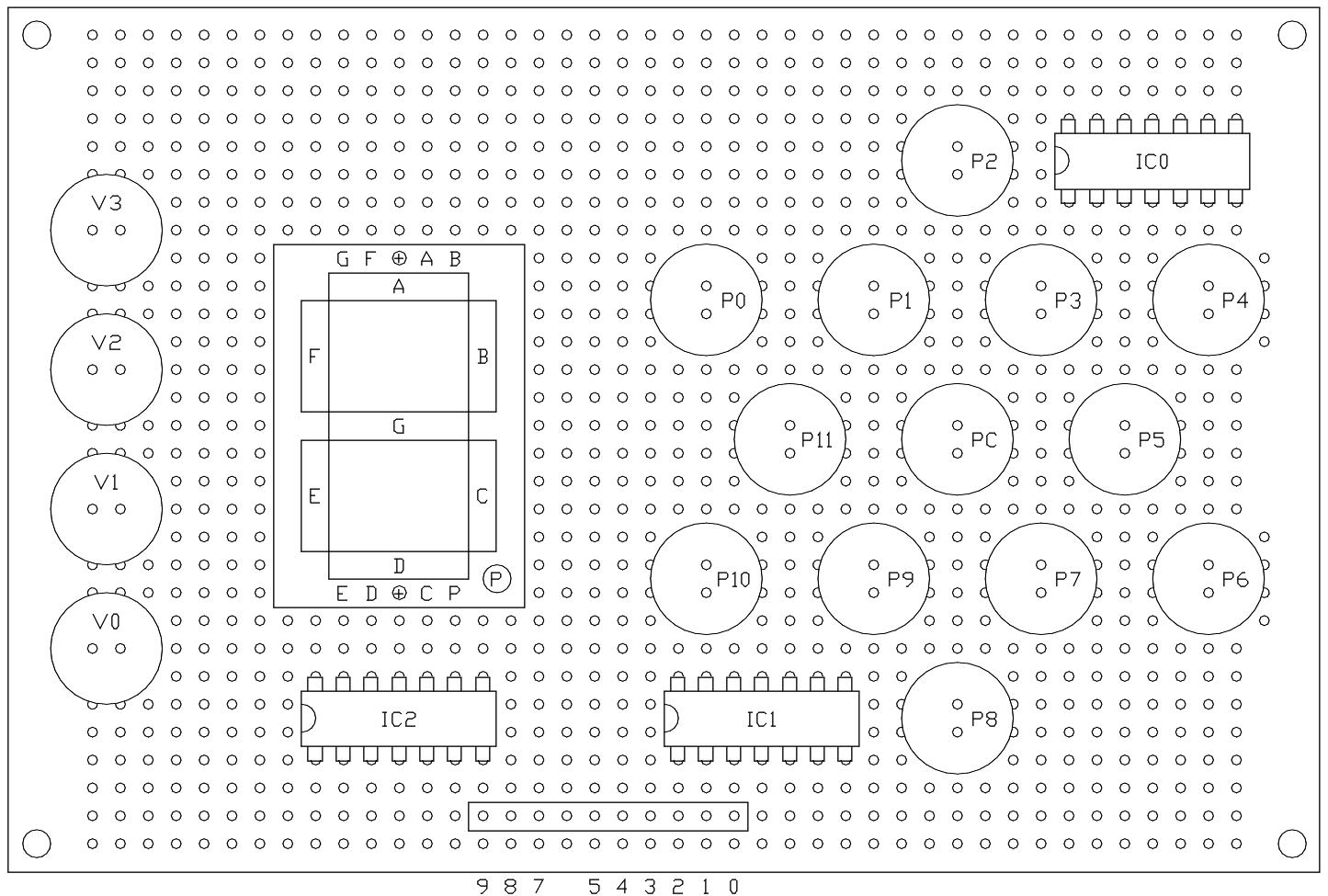

Here's a precision view of the board as I would probably lay it out now. I only put the octave display higher on mine because I didn't feel like moving IC2.

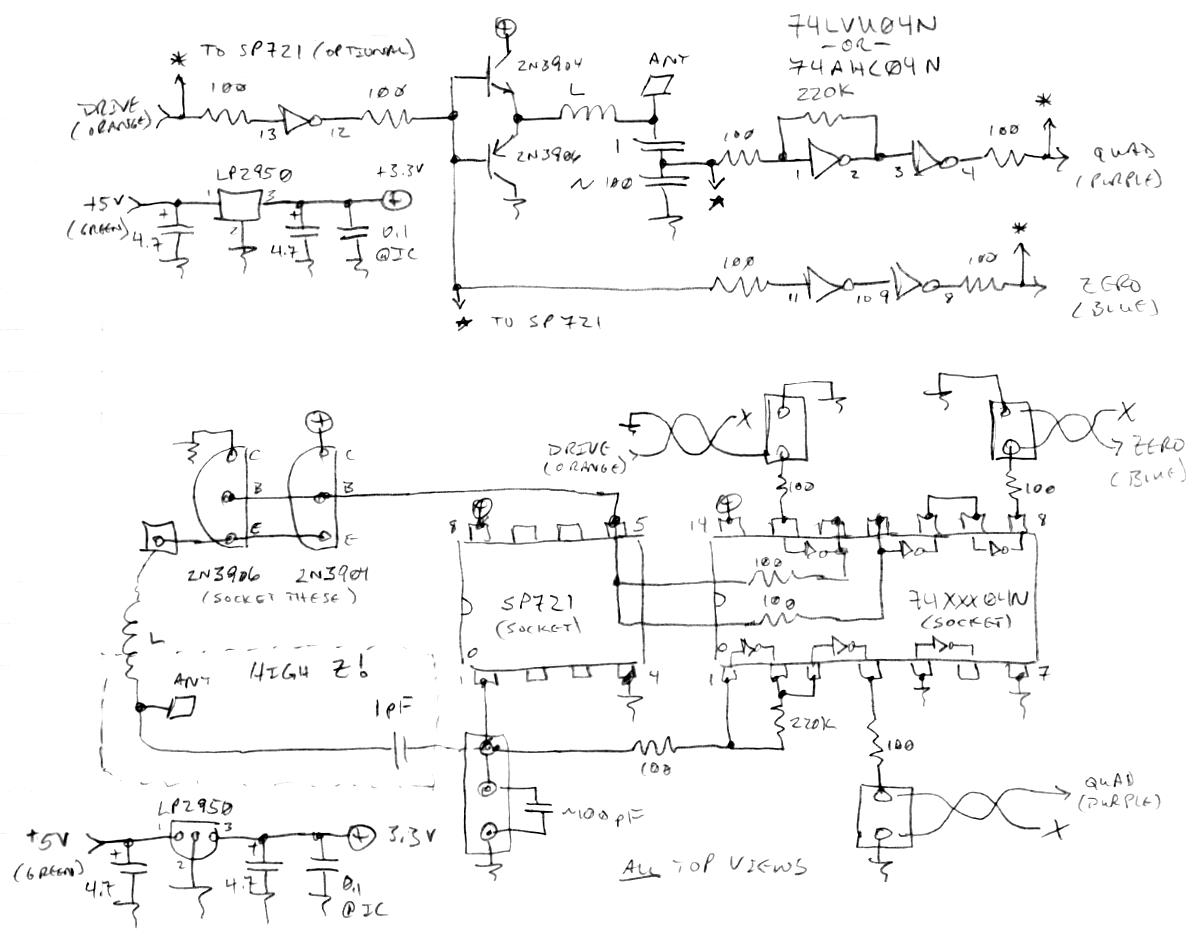

The schematic. I would swap SD0 and SD2 at the connector just to keep things clearer at hookup. FPGA pins can always be easily relocated too.

Honestly, I rarely consult the octave display, so it could probably be a lot smaller. It would be an interesting experiment to see how small the note display LEDs and star pattern could be made and still have it as readable and effective as the 10mm here.

The volume display is more useful than I thought it would be, giving visual feedback on things like knee point setting and the like.

What's really nice about the note display is, after you use it for a while, when you're picking out melodies by ear you can easily "see" what the key of the song is just by the pattern the notes take. It's sort of like playing the guitar, where it's more about the relative patterns the notes make on the fretboard than it is about the specific notes themselves. And the tuner UI page has a note offset knob, so you can play anything in the key of C tuner-wise until you get used to the other patterns - there are obviously 2 and their rotations.

I haven't used pitch preview and I'm thinking I probably never will. Even when I could clearly hear what my EW was doing pitch-wise, I'd always wander off into the weeds when playing unaccompanied. That literally never happens to me now with the tuner. Pitch correction helps too, but I'd say 90% of it is the precise pitch feedback the tuner provides. Without the tuner I probably would have given up on the hope of playing with any level of precision by now. And my ear isn't all that bad (after decades of tuning my guitar and singing). People without a really good pitch sense must spend a fair amount of time more or less lost on a conventional Theremin.

And I say the above not to piss anyone off, nor to make them feel bad about their Theremin, nor to blow my own horn. I frankly am a bit shocked at how much the note display improves playability, but people are different and so YYMV here as in all things.