I've noticed that new small but powerful Teensy series MCU board Teensy 4.0 became available recently at cost of $19.95.

Looks like ideal for Open.Theremin core replacement.

Benchmarks:

Technical Specifications

* ARM Cortex-M7 at 600 MHz

* 1024K RAM (512K is tightly coupled)

* 2048K Flash (64K reserved for recovery & EEPROM emulation)

* 2 USB ports, both 480 MBit/sec

* 3 CAN Bus (1 with CAN FD)

* 2 I2S Digital Audio

* 1 S/PDIF Digital Audio

* 1 SDIO (4 bit) native SD

* 3 SPI, all with 16 word FIFO

* 3 I2C, all with 4 byte FIFO

* 7 Serial, all with 4 byte FIFO

* 32 general purpose DMA channels

* 31 PWM pins

* 40 digital pins, all interrrupt capable

* 14 analog pins, 2 ADCs on chip

* Cryptographic Acceleration

* Random Number Generator

* RTC for date/time

* Programmable FlexIO

* Pixel Processing Pipeline

* Peripheral cross triggering

* Power On/Off management

ARM Cortex-M7 brings many powerful CPU features to a true real-time microcontroller platform.

Cortex-M7 is a dual-issue superscaler processor, meaning M7 can execute 2 instructions per clock cycle, at 600 MHz! Of course, executing 2 simultaneously depends upon the compiler ordering instructions and registers. Initial benchmarks have shown C++ code compiled by Arduino tends to achieve 2 instructions about 40% to 50% of the time while performing numerically intensive work using integers and pointers.

Cortex-M7 is the first ARM microcontroller to use branch prediction. On M4, loops and other code which much branch take 3 clock cycles. With M7, after a loop has executed a few times, the branch prediction removes that overhead, allowing the branch instruction to run in only a single clock cycle.

Tightly Coupled Memory is a special feature which allows Cortex-M7 fast single cycle access to memory using a pair of 64 bit wide buses. The ITCM bus provides a 64 bit path to fetch instructions. The DTCM bus is actually a pair of 32 bit paths, allowing M7 to perform up to 2 separate memory accesses in the same cycle. These extremely high speed buses are separate from M7's main AXI bus, which accesses other memory and peripherals. 512K of memory can be accessed as tightly coupled memory. Teensyduino automatically allocates your Arduino sketch code into ITCM and all non-malloc memory use to the fast DTCM, unless you add extra keywords to override the optimized default.

Memory not accessed on the tightly coupled buses is optimized for DMA access by peripherals. Because the bulk of M7's memory access is done on the 2 tightly coupled buses, powerful DMA-based peripherals have excellent access to the non-TCM memory for highly efficient I/O.

Teensy 4.0's Cortex-M7 processor includes a floating point unit (FPU) which supports both 64 bit "double" and 32 bit "float". With M4's FPU on Teensy 3.5 & 36, and also Atmel SAMD51 chips, only 32 bit float is hardware accelerated. Any use of double, double functions like log(), sin(), cos() means slow software implemented math. Teensy 4.0 executes all of these with FPU hardware.

512K is mostly enough for reverb.

600MHz floating point processing is enough for audio DSP algorithms.

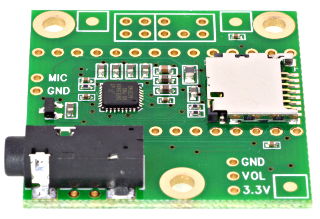

There is easy to use audio board which provides stereo 16bit 44100Hz audio I/O with headphones amplifier and Line In/Line Out. Cost: $13.75

Overclocking of MCU to 900-960MHz seems ok with heatsink.

I'm going to check for possible timer resolutions which can be used for theremin sensor frequency measure.

There are S/PDIF input and output pins.

I hope it would be possible to simple solder optical transmitter and receiver (like EVERLIGHT PLT133/PLR135) to have digital audio i/o.

For theremin sensor, we can use si5351 clock generator breakout for reference clocks + D-triggers (+ optional dividers) for heterodyning conversion of oscillator frequencies to easy measurable frequencies. Fast MCU should have good timer resolution for frequency measurement.

USB host connector can be added for connection of some extensions.

USB slave interface used for programming and power may provide USB slave devices as well - e.g. MIDI interface.

4 wire SPI/SDIO may be used for SD card interface.

So far, I've ordered Teensy 4, audio board for T4 (from PJRC), and 3.2" capacitive touch screen (ILI9341 spi interface, i2c for touch), and si5351 clock gen breakout - for experiments.