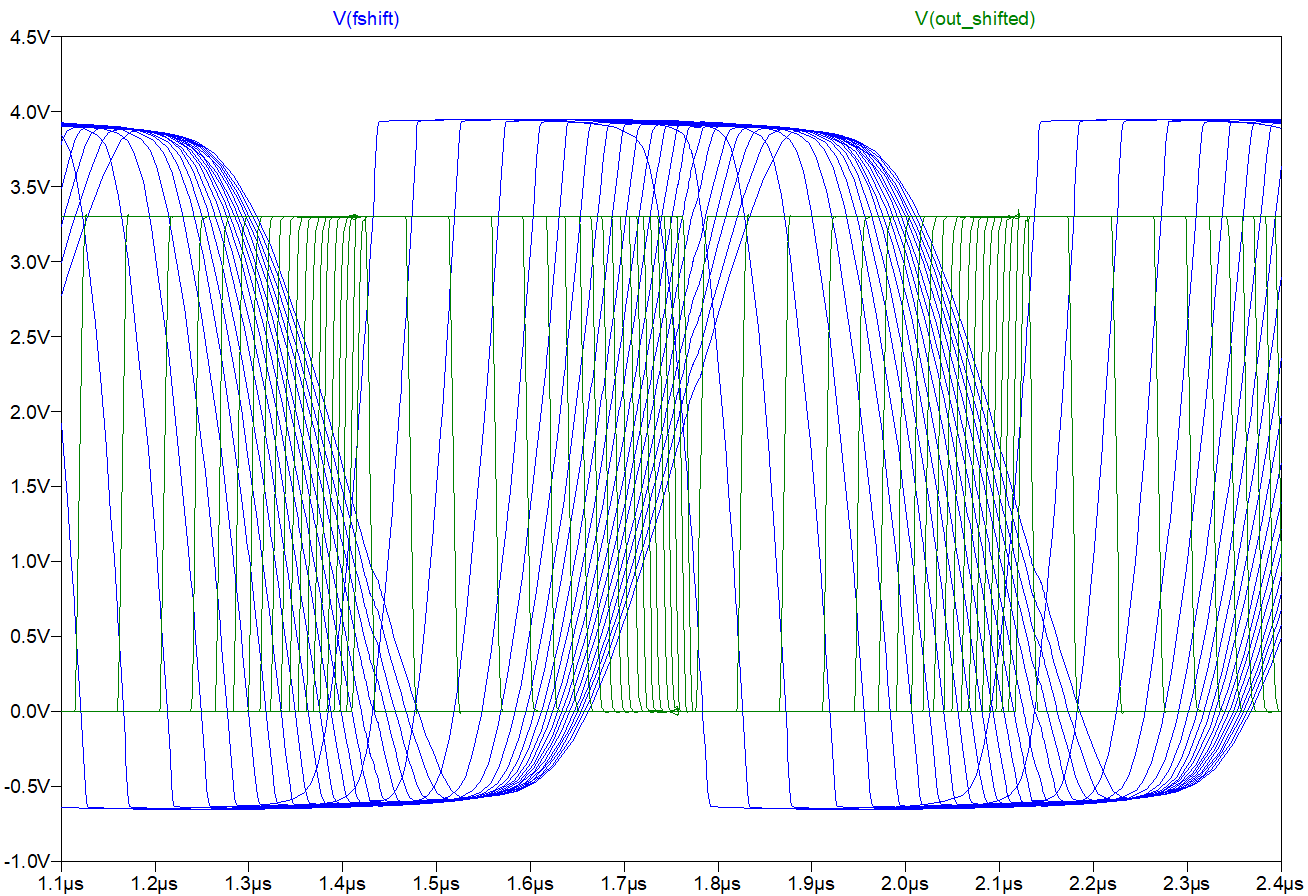

Collected data from RC delay between output and input.

It's not "dithered", but looks like alternating between two values with small frequency.

Pairs of raising pos, falling pos - captured for each cycle (~690KHz).

137 29 137 29 137 29 137 29 137 29 138 29 138 29 138 29 138 29 138 29 138 29 138 29 138 29 138 29 138 29 138 29 138 29 138 29 138 29 138 29 138 29 138 29 137 29 137 29 137 29 137 29 137 29 137 29 137 29 137 29 138 29 138 29 138 29 138 29 138 28 138 28 138 28 138 28 138 28 138 28 138 28 138 28 138 28 138 29 138 29 138 29 138 29 137 29 137 29 137 29 137 29 137 29 137 29 137 29 137 29 137 29 137 29 137 29 137 29 137 29 137 29 137 29 137 29 137 29 137 29 137 29 137 29 137 29 137 29 137 29 137 29 137 29 138 29 138 29 138 29 138 29 138 29 138 29 138 29 138 29 138 29 138 29 138 29 138 29 138 29 138 29 138 29 138 29 138 29 137 29 137 29 137 29 137 29 137 29 137 29 137 29 137 29 138 29 138 29 138 29 138 29 138 28 138 28 138 28 138 28 138 28 138 28 138 28 138 28 138 29 138 29 138 29 138 29 138 29 137 29 137 29 137 29 137 29 137 29 137 29 137 29 137 29 138 29 138 29 138 29 138 29 138 29 138 29 138 29 138 29 138 29 138 29 138 29 138 29 138 29 138 29 138 29 138 29 138 29 137 29 137 29 137 29 137 29 137 29 137 29 137 29 137 29 137 29 137 29 137 29 137 29 137 29 137 29 137 29 137 29 137 29 137 29 137 29 137 29 137 29 137 29 137 29 137 29 137 29 138 29 138 29 138 29 138 29 138 30 138 30 138 30 138 30 137 30 137 30 137 30 137 30 137 29 137 29 137 29 137 29 137 29 137 29 137 29 137 29 137 29 137 29 137 29 137 29 137 29 138 29 138 29 138 29 138 29 138 29 138 29 138 29 138 29 137 29 137 29 137 29 137 29 137 29 137 29 137 29 137 29 138 29 138 29 138 29 138 29 138 29 138 29 138 29 138 29 138 29 138 29

There is internal feature in Teensy 4 PWM - similar to dithering, can be applied to output signal raising and falling edge position as fractional part (5 bits).

It's not oversampling. It's a kind of dithering - 1 is added to position value for A of 32 cycles - if fraction is set to A/32.

Not sure if it's dithered or goes as single piece once per 32 cycles.