"Thanks dewster for links at the first page of this thread. Quick access is very handy. Truly, this topics is a kind of encyclopedia." - ILYA

What a nice thing to say, thanks ILYA! The index is in need of some updating...

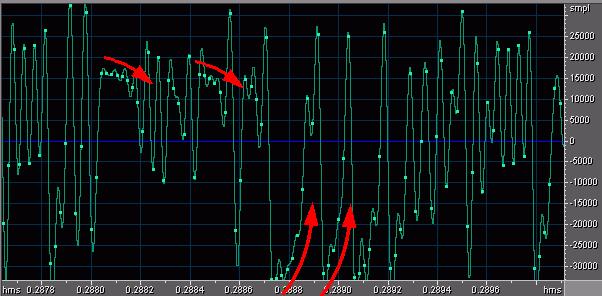

"Experimenting with different polynomials, I have discovered the following thing. Some polynomials, C0FEBABE for example  , produces the flat spectrum curve even without the "whitening" filter."

, produces the flat spectrum curve even without the "whitening" filter."

This is completely unexpected! I naively thought that LFSR output spectrum was a "thing" and that's it. Nowhere have I read anything that would lead me to believe otherwise. Though the Galois XORing seems like it would whiten things up much more than the single LSb (or MSb) flip (50% of the time) of the Fibonacci method.

The output sequences look qualitatively somewhat different. I wonder if there are applications / instances where this difference might be apparent? I'll have to try it out in the D-Lev code.

A code snippet is worth a million words! So:

IF (MSb is set) : XOR with 0xE0000200, shift left, set the LSb

ELSE : shift left

It seems MSb(input) == LSb(output) is always true? And after being tested, it seems MSb(input) is unused? So the polynomial could be 0x60000200 with no difference in functionality? If so, I believe you could check the sign to conditionally do the XOR with 0x60000200 (which would preserve the MSb), then use a left rotate instead of a shift to automatically generate the LSb?